Silizium-Wafer werden immer dünner

Infineon erhöht mit einer Dicke von nur 20 Mikrometern die Effizienz von Leistungshalbleiter.

Nach der Ankündigung der weltweit ersten 300-Millimeter-Galliumnitrid (GaN)-Wafer-Technologie für Leistungselektronik und der Eröffnung der weltweit größten 200-Millimeter-„Siliziumcarbid (SiC) Power Fab“ in Kulim, Malaysia, hat das Unternehmen Infineon Technologies einen weiteren Rekord in der Halbleitertechnologie aufgestellt. Mit einer Dicke von nur zwanzig Mikrometern gelang Herstellung und Verarbeitung der dünnsten Silizium (Si)-Leistungshalbleiter-Wafer, die jemals in einer hochskalierten Halbleiterfabrik hergestellt wurden. Die Silizium-Dünnwafer sind etwa halb so dick wie die aktuell fortschrittlichsten Wafer.

„Die weltweit dünnsten Silizium-Wafer sind ein Beleg dafür, dass wir bei Infineon die technischen Grenzen der Leistungs-Halbleitertechnologie bis ans Limit treiben, um unseren Kunden erstklassigen Mehrwert zu bieten“, sagt Jochen Hanebeck, CEO von Infineon Technologies. „Der Durchbruch in der Ultradünnwafer-Technologie ist ein bedeutender Schritt vorwärts im Bereich energieeffizienter Stromversorgungslösungen und hilft uns, das volle Potenzial der globalen Trends Dekarbonisierung und Digitalisierung auszuschöpfen.“

Die Innovation wird laut Aussage des Unternehmens dazu beitragen, die Energieeffizienz, die Leistungsdichte und die Zuverlässigkeit in Stromversorgungslösungen für KI-Rechenzentren, Consumer-, Motorsteuerungs- und Computing-Anwendungen signifikant zu erhöhen. Die Halbierung der Waferdicke verringert den Substratwiderstand um fünfzig Prozent. Leistungsverluste in Power-Systemen können so im Vergleich zu Lösungen auf Basis von konventionellen Silizium-Wafern mit einer Dicke von vierzig bis sechzig Mikrometern um mehr als 15 Prozent reduziert werden. Für die Stromversorgung fortschrittlicher KI-Server-Anwendungen, bei denen die steigende Energienachfrage durch höhere Stromstärken angetrieben wird, ist dies besonders wichtig. In KI-Rechenzentren müssen Spannungen von 230 Volt auf eine Prozessor-Spannung von unter 1,8 Volt reduziert werden. Die Ultradünnwafer-Technologie fördert ein vertikales Stromversorgungs-Design, das auf der Trench-MOSFET-Technologie basiert und eine sehr nahe Positionierung am KI-Chip-Prozessor ermöglicht, wodurch Leistungsverluste reduziert und die Gesamteffizienz verbessert werden.

„Die neue Ultradünnwafer-Technologie befeuert unsere Ambition, verschiedenste KI-Server-Konfigurationen auf die energieeffizienteste Weise zu versorgen, vom Stromnetz bis hin zum Prozessorkern“, sagt Adam White von Infineon. Da der Energiebedarf für KI-Rechenzentren rapide ansteige, gewinne Energieeffizienz immer mehr an Bedeutung. Um die technischen Hürden bei der Reduzierung der Waferdicke auf zwanzig Mikrometer zu überwinden, mussten die Ingenieure einen einzigartigen Wafer-Schleifansatz entwickeln, da das Metallgehäuse, das den Chip auf dem Wafer hält, dicker als zwanzig Mikrometer ist. Dies beeinflusst die Handhabung und Verarbeitung der Rückseite des Wafers erheblich.

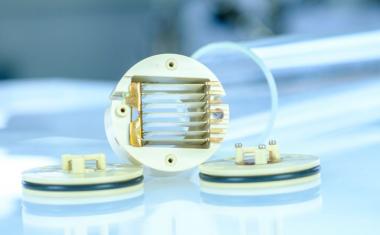

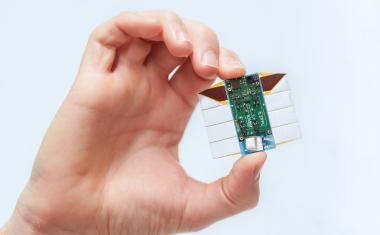

Außerdem haben Herausforderungen wie Wafer-Krümmung und Wafer-Separation einen großen Einfluss auf die Backend-Montageprozesse, die die Stabilität und erstklassige Robustheit der Wafer sicherstellen. Der Dünnwafer-Prozess gewährleistet eine nahtlose Integration der neuen Technologie in existierende Hochvolumen-Silizium-Produktionslinien. Es fallen keine zusätzlichen Fertigungskosten an, um höchste Produktionserträge und Liefersicherheit zu garantieren. Infineon hat die Technologie bereits mit Kunden qualifiziert und auf seine Integrated Smart Power Stages (DC-DC-Wandler) angewendet. Das Unternehmen plant, die Produktion von Ultradünnwafern zu erhöhen und bestehende konventionelle Silizium-Wafer für Niedervolt-Stromversorgungen innerhalb der kommenden drei bis vier Jahre durch den 20-Mikrometer-Prozess zu ersetzen.

Infineon / JOL